English

English  Español

Español Português

Português русский

русский Français

Français 日本語

日本語 Deutsch

Deutsch tiếng Việt

tiếng Việt Italiano

Italiano Nederlands

Nederlands ภาษาไทย

ภาษาไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা ভাষার

বাংলা ভাষার Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türkçe

Türkçe Gaeilge

Gaeilge العربية

العربية Indonesia

Indonesia Norsk

Norsk تمل

تمل český

český ελληνικά

ελληνικά український

український Javanese

Javanese فارسی

فارسی தமிழ்

தமிழ் తెలుగు

తెలుగు नेपाली

नेपाली Burmese

Burmese български

български ລາວ

ລາວ Latine

Latine Қазақша

Қазақша Euskal

Euskal Azərbaycan

Azərbaycan Slovenský jazyk

Slovenský jazyk Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski

칩 IC가 다음 전자 제품 제작의 위험을 어떻게 줄일 수 있습니까?

추상적인

A 칩 IC BOM에서 가장 작은 항목인 경우가 많지만 지연, 현장 오류 및 숨겨진 비용의 가장 큰 원인이 될 수 있습니다. "실험실에서는 성공했지만 현실에서는 실패"하는 제품, 갑작스러운 구성 요소 교체 또는 갑작스러운 수명 종료 알림을 처리해 본 적이 있다면 프로젝트가 얼마나 빨리 진행될 수 있는지 이미 알고 계실 것입니다.

이 기사에서는 애플리케이션을 선택, 검증 및 통합하는 실제적인 방법을 자세히 설명합니다.칩 IC따라서 프로토타입 제작뿐만 아니라 생산 과정에서도 제품이 안정적입니다. 선택을 위한 명확한 체크리스트, 신뢰성 가드레일, 위조 방지를 위한 간단한 검증 작업 흐름, PCBA 통합에 대한 제조 중심 접근 방식을 얻을 수 있습니다. 그 과정에서 팀이 일반적으로 다음 지원을 통해 이러한 문제를 해결하는 방법을 공유하겠습니다.심천 인사말 전자 유한 공사특히 시간, 수율, 장기 공급이 위태로운 경우에는 더욱 그렇습니다.

목차

- 개요

- 칩 IC 결정이 큰 결과를 가져오는 이유

- 실제 프로젝트에서 "Chip IC"가 다루는 내용

- 고객의 불만 사항 및 일반적으로 해결 방법

- 재작업을 방지하는 칩 IC 선택 체크리스트

- 예상치 못한 생산량 없이 PCBA에 통합

- 실제로 중요한 품질 및 신뢰성 관리

- 안전을 훼손하지 않는 비용 및 공급망 전략

- FAQ

- 다음 단계

개요

- 기능, 패키지 및 수명주기 위험 전반에 걸쳐 "칩 IC"가 의미하는 바를 정의합니다.

- 일반적인 실패 모드를 특정 예방 단계에 매핑

- 전기, 기계, 환경, 제조 제약 사항을 다루는 선택 체크리스트를 사용하세요.

- 레이아웃, 조립, 프로그래밍 및 테스트를 염두에 두고 IC를 통합합니다.

- 시제품부터 양산까지 실질적인 검증 및 신뢰성 관리 적용

- 2차 소스 및 변경 제어 계획을 통해 비용과 리드 타임의 균형을 유지하세요.

칩 IC 결정이 큰 결과를 가져오는 이유

팀은 일반적으로 다음 중 하나를 선택합니다.칩 IC빠른 비교를 바탕으로 “스펙과 예산에 맞는가?” 좋은 시작이지만 배송, 온도 변화, ESD 이벤트, 긴 듀티 사이클, 예측할 수 없는 작업을 수행하는 실제 사용자를 견뎌야 하는 무언가를 구축하는 경우에는 충분하지 않습니다.

실제로 종이에 적힌 "올바른" IC는 여전히 문제를 일으킬 수 있습니다.

- 일정 위험긴 리드타임이나 갑작스러운 부족으로 인해

- 수확량 손실조립 민감도, 습기 문제 또는 한계 설치 공간으로부터

- 현장 오류열 스트레스, ESD 또는 경계선 전력 무결성으로부터

- 재자격의 고통적절한 관리 없이 부품을 교체한 경우

목표는 완벽함이 아니라 예측 가능성입니다. 당신은칩 IC프로토타입부터 생산까지 제품이 안정적으로 유지되도록 엔지니어링, 제조 및 공급망을 연계하는 전략입니다.

실제 프로젝트에서 "Chip IC"가 다루는 내용

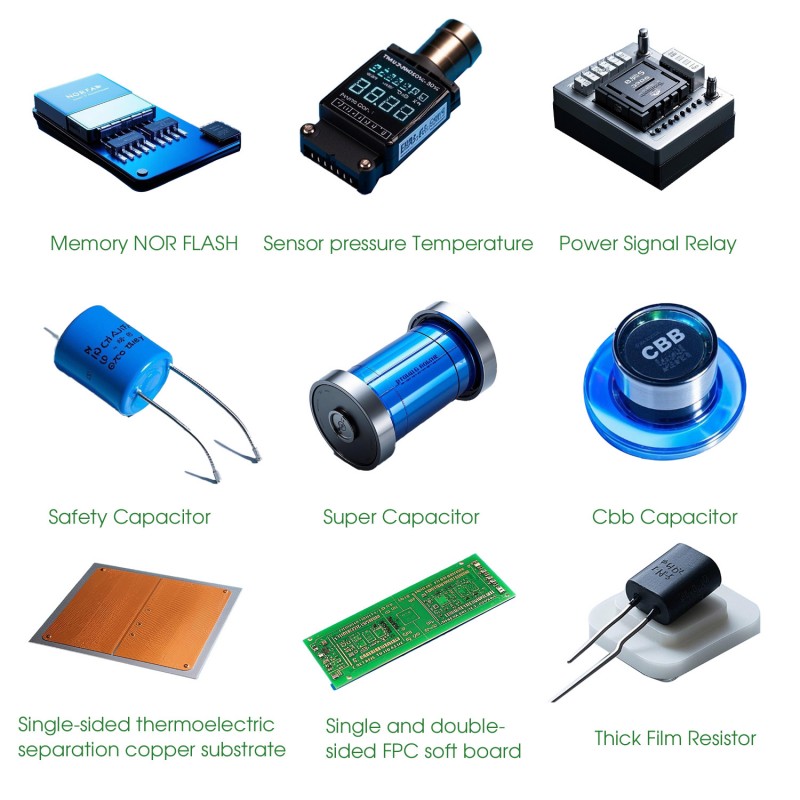

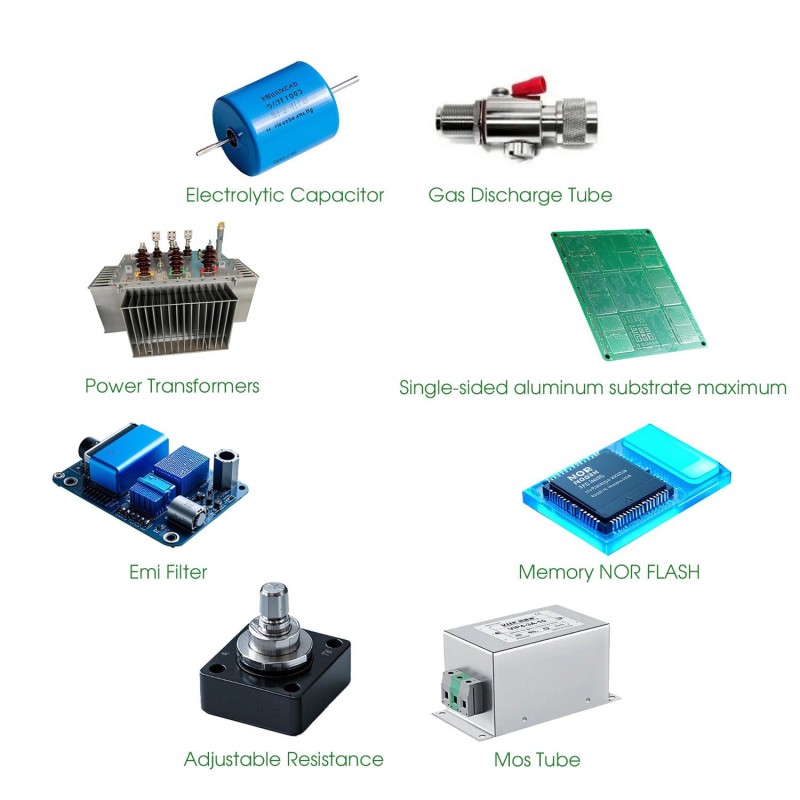

“칩 IC"는 광범위하고 실용적인 우산입니다. 제품에 따라 다음을 의미할 수 있습니다.

- MCU 및 프로세서(제어 로직, 펌웨어, 연결 스택)

- 전력 IC(PMIC, DC-DC 컨버터, LDO, 배터리 관리)

- 아날로그 및 혼합 신호 IC(ADC/DAC, 연산 증폭기, 센서 인터페이스)

- 인터페이스 및 보호 IC(USB, CAN, RS-485, ESD 보호 어레이)

- 메모리 및 스토리지(플래시, EEPROM, DRAM)

두 IC는 유사한 데이터시트 번호를 공유할 수 있으며 패키지 유형, 열 경로, 제어 루프 안정성, 레이아웃 민감도 또는 프로그래밍/테스트 요구 사항으로 인해 보드에서 여전히 다르게 동작할 수 있습니다. 이것이 바로 "사양 충족"이 결정의 한 단계일 뿐인 이유입니다.

고객의 불만 사항 및 일반적으로 해결 방법

고객이 가장 자주 제기하는 문제는 다음과 같습니다.칩 IC병목 현상이 발생하고 실제로 위험을 줄이는 수정 사항이 됩니다.

-

문제점 1: "정확한 IC를 안정적으로 소싱할 수 없습니다."

수정: 승인된 대체 목록을 조기에 정의하고, 변경 제어 프로세스를 잠그고, 엄격한 전기 + 기능 테스트 계획을 통해 대체를 검증합니다. -

문제점 2: "프로토타입은 작동하지만 생산 수율이 불안정합니다."

수정: 설치 공간 및 어셈블리 제약 조건(스텐실, 페이스트, 리플로우 프로필, MSL 처리)을 검토한 다음 한계 동작을 포착하는 경계 테스트를 추가합니다. -

문제점 3: "우리는 위조 또는 재생 부품에 대해 걱정합니다."

수정 사항: 수신 확인 작업 흐름(추적성, 육안 검사, 표시 확인, 샘플 전기 테스트)을 구현하고 통제된 조달 채널을 사용합니다. -

문제점 4: "부하 또는 온도에 따라 전원 문제가 나타납니다."

수정 사항: 전력 무결성과 열을 최우선 요구 사항으로 처리합니다. 일반적인 조건뿐만 아니라 최악의 코너도 검증합니다. -

문제점 5: "가져오고 디버깅하는 데 시간이 낭비됩니다."

수정: 테스트용 설계(해당되는 경우 테스트 지점, 경계 스캔) 및 제조 과정의 일부로 프로그래밍/펌웨어 로딩 계획(나중에 고려하지 않음)

단일 파트너가 선택 지원, PCBA 통합, 소싱 규율 및 생산 테스트를 조정하기를 원하는 많은 팀은 다음과 같이 작업합니다.심천 인사말 전자 유한 공사왜냐하면 대부분의 "깜짝 실패"가 숨어 있는 핸드오프 공백을 줄이기 때문입니다.

재작업을 방지하는 칩 IC 선택 체크리스트

장치를 잠그기 전에 이 체크리스트를 사용하십시오.칩 IC당신의 디자인에. 빠른 데이터시트 훑어보기에는 나타나지 않는 문제를 포착하도록 설계되었습니다.

- 전기 마진:최악의 전압, 전류, 온도 및 허용 오차 스택을 확인한 다음 실제 부하 동작에 대한 여유를 추가합니다.

- 패키지 및 조립 적합성:패키지 가용성(QFN/BGA/SOIC 등), 설치 공간 견고성, 조립업체가 피치 및 열 패드 요구 사항을 처리할 수 있는지 여부를 검증합니다.

- 열 경로:최악의 경우 접합 온도를 평가하고 현실적인 열 경로(구리 타설, 비아, 공기 흐름 가정)가 있는지 확인합니다.

- ESD 및 일시적 노출:실제 노출(케이블, 사용자 접촉, 유도 부하)을 매핑하고 외부 보호 IC 또는 필터링이 필요한지 결정합니다.

- 펌웨어/프로그래밍 요구 사항:프로그래밍 인터페이스, 보안 요구 사항, 생산 프로그래밍이 인라인으로 수행되는지 오프라인으로 수행되는지 여부를 확인합니다.

- 테스트 가능성:생산에서 측정할 항목(파워 레일, 주요 파형, 통신 핸드셰이크, 센서 확인)을 정의하고 보드가 이를 지원하는지 확인합니다.

- 수명주기 위험:예상 수명을 확인하고 필요한 경우 대체 제품 및 최종 구매에 대한 계획을 수립합니다.

- 문서화 분야:부품 번호, 패키지 변형 및 개정 규칙을 동결하여 대체품이 자동 실패가 되지 않도록 합니다.

이 목록에서 한 가지만 수행한다면 다음과 같이 하십시오.칩 IC(전기 범위, 패키지, 자격 기대치, 프로그래밍 방법) 모든 대안이 이를 충족할 수 있음을 입증하십시오.

예상치 못한 생산량 없이 PCBA에 통합

A 칩 IC단독으로 실패하지 않습니다. 실제 제조 공정에서 보드, 인클로저 내부에서 실패합니다. 통합은 신뢰성을 얻거나 잃는 곳입니다.

- 레이아웃은 원하는 것보다 더 중요합니다.민감한 IC(고속, 스위칭 전력, RF)는 "정확"하지만 라우팅, 접지 또는 디커플링이 엉성할 경우 불안정할 수 있습니다.

- 디커플링은 장식적이지 않습니다.커패시터를 의도한 대로 배치하고 루프 영역을 최소화하며 최악의 부하에서 리플 및 과도 응답을 검증합니다.

- 리플로우 및 MSL 처리:습기에 민감한 포장은 보관 및 굽기 규칙을 따르지 않으면 깨지거나 갈라질 수 있습니다.

- 스텐실 및 페이스트 인쇄:미세 피치 패키지 및 열 패드에는 삭제 표시, 브리징 또는 보이딩을 방지하기 위해 페이스트 제어가 필요합니다.

- 프로그래밍 흐름:설비 액세스를 계획하고 라인 끝에서 펌웨어 버전과 구성을 확인하는 방법을 정의합니다.

좋은 습관은 첫 번째 파일럿 실행을 학습 실험처럼 다루는 것입니다. 결함 유형, 위치 및 조건을 추적한 다음 볼륨을 확장하기 전에 레이아웃을 조정하거나 업데이트를 처리하여 루프를 닫습니다.

실제로 중요한 품질 및 신뢰성 관리

신뢰성은 분위기가 아닙니다. 이는 현장에서 가장 흔히 볼 수 있는 실패 모드를 파악하는 일련의 검사입니다. 아래 표는 실용적인 메뉴입니다. 제품의 위험 프로필과 일치하는 항목을 선택하세요.

| 제어 | 무엇을 잡는가 | 실질적인 구현 |

|---|---|---|

| 수신 확인(샘플링) | 위조, 잘못된 변형, 발언 | 추적성 검사 + 육안 검사 + 기본 전기 ID 테스트 |

| 파워 레일 마진 테스트 | 전압 저하, 불안정한 조정기, 부하 과도 현상 | 최소/최대 입력, 최대 부하, 온도 코너에서 테스트 |

| 열 흡수/번인(필요에 따라) | 초기 고장, 한계 솔더 조인트 | 정의된 기간 동안 가열 상태에서 기능 테스트 실행 |

| ESD/일시적 검증 | 사용자 터치 실패, 케이블 이벤트, 유도성 반동 | I/O에 현실적인 이벤트를 적용하고 래치업이나 재설정이 없는지 확인합니다. |

| 펌웨어/구성 확인 | 잘못된 펌웨어, 잘못된 지역 구성, 교정 누락 | 줄 끝 다시 읽기 + 버전 로깅 + 통과/실패 규칙 |

제품이 열악한 환경에 배송되는 경우 열 및 과도 검증을 우선시하십시오. 제품이 대량으로 배송되는 경우 테스트 가능성과 수신 검증에 우선순위를 두어 배치 전반에 걸쳐 결함이 증가하지 않도록 하세요.

안전을 훼손하지 않는 비용 및 공급망 전략

비용 통제는 현실적이고 필요합니다. 하지만 약 1년 정도의 비용 절감칩 IC추적성을 제거하거나, 들어오는 수표를 약화시키거나, 통제되지 않은 대체를 장려하는 경우 조용히 위험을 초래할 수 있습니다.

- "허용되는 대체품"을 서면으로 정의하십시오.동일한 전기 등급, 동일한 패키지, 동일한 자격 기대치. 그 밖의 모든 것은 재검증을 트리거합니다.

- 2계층 소싱 계획을 사용합니다.안정성을 위한 기본 채널; 만일의 사태를 대비한 2차 조치 - 조사 및 추적 가능.

- 대체품을 따뜻하게 유지하세요:부족이 발생할 때까지 기다리지 마십시오. 지금 대안으로 소규모 배치를 구축하고 승인 테스트를 실행하십시오.

- 로트 및 날짜 코드 추적:결함 클러스터가 나타나는 경우 문제를 빠르게 격리하는 데 도움이 됩니다.

- 수명주기 이벤트 계획:제품 지원 기간 내에 IC의 수명이 다할 가능성이 있는 경우 조기에 마이그레이션 경로를 설계하세요.

제정신을 유지하는 실용적인 방법은 엔지니어링 규칙(허용되는 것)과 구매 규칙(구매가 허용되는 것)을 연결하여 시스템이 마감 기한 압박으로 인해 표류하지 않도록 하는 것입니다.

FAQ

Q: 칩 IC를 선택할 때 가장 먼저 무엇을 검증해야 합니까?

에이:최악의 전기 마진과 패키지/제조 적합성부터 시작하십시오. IC를 안정적으로 조립할 수 없거나 최악의 부하에서 뜨거워지면 다른 모든 것이 손상 제어가 됩니다.

Q: 위조 칩 IC의 위험을 줄이려면 어떻게 해야 합니까?

에이:추적성을 요구하고, 통제되지 않은 현물 구매를 방지하고, 들어오는 샘플링 검사를 추가합니다(마킹, 포장 및 빠른 전기 검증). 위험도가 높은 빌드의 경우 샘플 크기를 늘리고 결과를 로트별로 기록하세요.

Q: 내 전원 IC가 평가 보드와 최종 보드에서 다르게 동작하는 이유는 무엇입니까?

에이:레이아웃, 접지 및 구성 요소 배치는 제어 루프 동작과 소음 환경을 변경하는 경우가 많습니다. 정확한 PCB, 정확한 로드 프로필 및 실제 배선/케이블을 사용하여 검증하십시오.

Q: 모든 제품에 번인이 필요합니까?

에이:항상 그런 것은 아닙니다. 번인(Burn-in)은 초기 실패로 인해 비용이 많이 들거나 현장 접근이 어려울 때 또는 파일럿 실행에서 한계 결함이 발견될 때 가장 유용합니다. 그렇지 않으면 강력한 기능 테스트와 수신 검증이 더 효율적일 수 있습니다.

Q: IC 리드 타임으로 인한 지연을 방지하려면 어떻게 해야 합니까?

에이:대체 항목을 조기에 잠그고, 강제로 전환하기 전에 검증하고, 구매 규칙을 엔지니어링 승인 목록에 맞춰 유지하여 대체 항목이 조용히 발생하지 않도록 하세요.

Q: 칩 IC를 "생산 준비" 상태로 만드는 이유는 무엇입니까?

에이:프로토타입 데모를 통과하는 것만이 아닙니다. 생산 준비가 완료되었다는 것은 추적성을 통해 IC를 소싱할 수 있고 안정적인 수율로 조립할 수 있으며 일관된 최종 라인 테스트를 통과하고 환경 및 일시적인 조건에서도 견딜 수 있음을 의미합니다.

다음 단계

당신이 원한다면칩 IC도박을 멈추고 선택, 소싱, 조립 및 테스트를 하나의 연결된 시스템으로 처리하기로 결정했습니다. 이것이 바로 "프로토타입 성공 → 파일럿 놀라움 → 생산 지연"이라는 고전적인 루프를 방지하는 방법입니다.

~에심천 인사말 전자 유한 공사, 우리는 팀이 선택 지원 및 PCBA 통합부터 검증 작업 흐름 및 생산 테스트에 이르기까지 칩 IC 불확실성을 통제된 계획으로 전환하도록 돕습니다. 부족, 수율 불안정 또는 신뢰성 문제에 직면한 경우 응용 프로그램, 대상 환경 및 볼륨을 알려주십시오. 실제적인 경로를 제안해 드리겠습니다.

더 적은 위험으로 더 빠르게 움직일 준비가 되셨나요?BOM과 요구 사항을 공유하고 저희에게 연락주세요 귀하의 제품에 맞는 안정적인 Chip IC 및 PCBA 전략을 논의하십시오.